Engenheiros da Universidade de Stanford, da Universidade Carnegie Mellon, da Universidade da Pensilvânia e do Instituto de Tecnologia de Massachusetts colaboraram com a SkyWater Technology, a maior fundição de semicondutores exclusivamente americana, para criar um novo chip de computador em camadas múltiplas. A equipe afirma que sua arquitetura pode marcar uma mudança significativa no hardware de IA e fortalecer a inovação em semicondutores domésticos.

Diferente da maioria dos chips atuais, que são principalmente planos e 2D, este protótipo é projetado para se elevar. Partes ultra finas são empilhadas como andares em um edifício alto, e a fiação vertical funciona como muitos elevadores rápidos que movimentam enormes quantidades de dados rapidamente. Com um número recorde de conexões verticais e um layout densamente entrelaçado que coloca as unidades de memória e de computação próximas umas das outras, o design evita lentidões que têm limitado o progresso em chips planos. Em testes de hardware e simulações, o chip 3D supera os chips 2D em cerca de uma ordem de magnitude.

Pesquisadores já haviam produzido chips 3D experimentais em laboratórios acadêmicos antes, mas a equipe afirma que esta é a primeira vez que um deles apresenta melhorias claras de desempenho e é produzido em uma fundição comercial. “Isso abre as portas para uma nova era de produção de chips e inovação,” disse Subhasish Mitra, professor William E. Ayer em Engenharia Elétrica e professor de ciência da computação na Universidade de Stanford, e investigador principal de um novo artigo que descreve o chip apresentado na 71ª Reunião Anual da IEEE International Electron Devices Meeting (IEDM). “Avanços como este são como chegamos às melhorias de desempenho de hardware de 1.000 vezes que os futuros sistemas de IA demandarão.”

Por Que os Chips Planos Enfrentam Dificuldades com a IA Moderna

Grandes modelos de IA, como ChatGPT e Claude, constantemente movimentam enormes volumes de dados entre a memória, que armazena informações, e as unidades de computação que processam esses dados.

Nos chips 2D convencionais, tudo está em uma superfície única e a memória é limitada e dispersa, forçando os dados a circularem por um pequeno número de caminhos longos e lotados. As partes de computação podem operar muito mais rápido do que os dados podem ser entregues, e o chip não consegue manter memória suficiente por perto. O resultado é frequente espera. Os engenheiros chamam esse problema de “muralha da memória”, onde a velocidade de processamento supera a capacidade do chip de fornecer dados.

Durante anos, os fabricantes de chips tentaram contornar a muralha da memória diminuindo transistores, os pequenos interruptores que realizam cálculos e armazenam dados, e empilhando cada vez mais deles em cada chip. Mas pesquisadores afirmam que essa abordagem está se aproximando de limites físicos rigorosos, conhecidos como a “muralha da miniaturização.”

O novo design visa superar ambos os limites construindo para cima. “Ao integrar memória e computação verticalmente, podemos mover muito mais informações de maneira mais rápida, assim como os bancos de elevadores em um prédio alto permitem que muitos residentes se desloquem entre os andares ao mesmo tempo,” disse Tathagata Srimani, professor assistente de engenharia elétrica e de computação na Universidade Carnegie Mellon, autor sênior do artigo, que iniciou o trabalho como pesquisador de pós-doutorado sob a orientação de Mitra.

“A muralha da memória e a muralha da miniaturização formam uma combinação mortal,” disse Robert M. Radway, professor assistente de engenharia elétrica e de sistemas na Universidade da Pensilvânia e coautor do estudo. “Atacamos isso de frente integrando memória e lógica de forma apertada e, em seguida, construindo para cima em densidade extremamente alta. É como Manhattan da computação – conseguimos acomodar mais pessoas em menos espaço.”

Como o Chip 3D Monolítico é Fabricado

Muitos esforços anteriores com chips 3D seguiram uma rota mais simples empilhando chips separados. Isso pode ajudar, mas as conexões entre as camadas costumam ser relativamente rústicas, limitadas em número e podem se tornar gargalos.

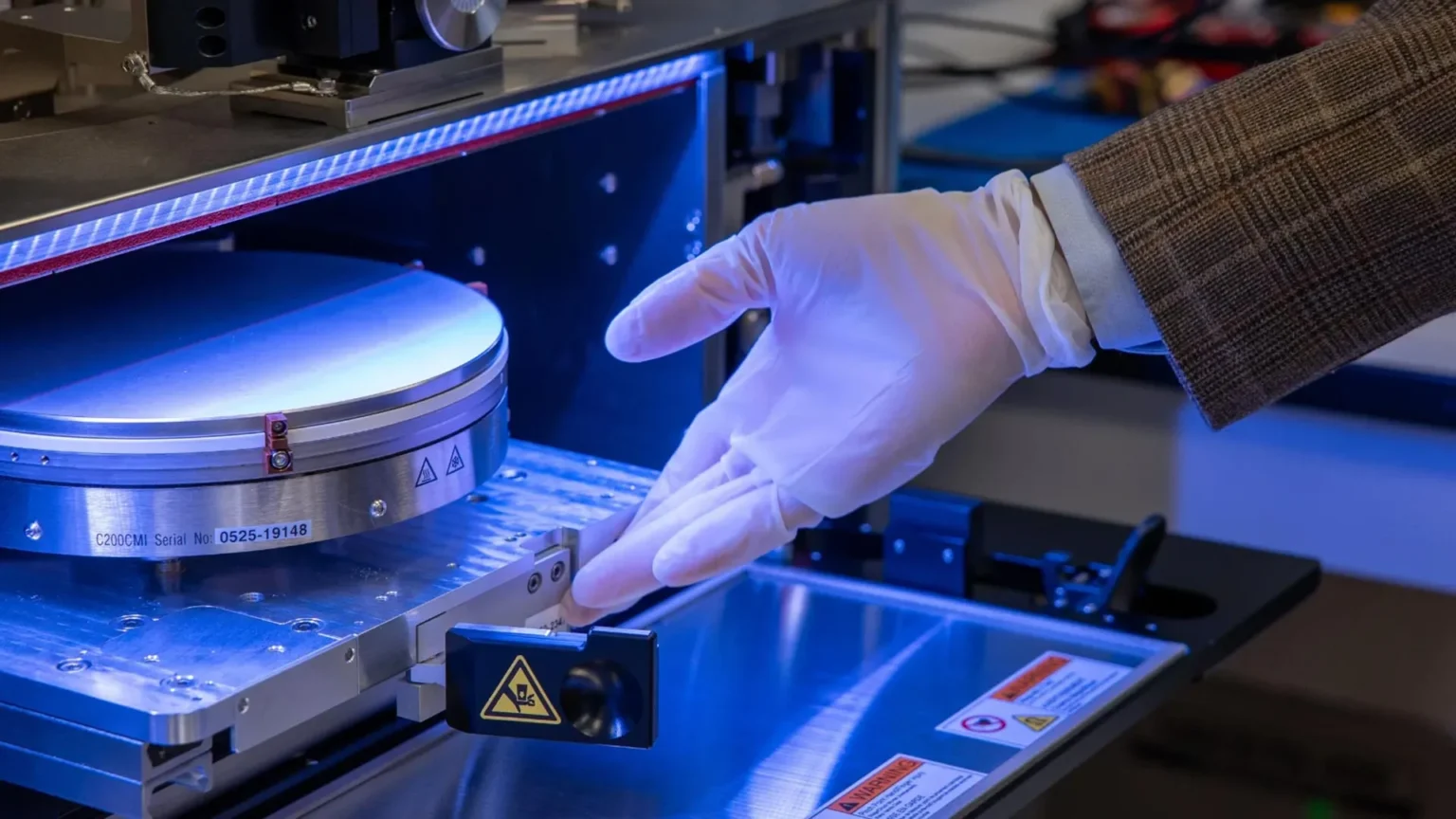

Esta equipe adotou uma abordagem diferente. Em vez de fabricar chips separados e uní-los, eles constroem cada nova camada diretamente em cima da anterior em um único fluxo contínuo. Este método, conhecido como integração 3D “monolítica”, utiliza temperaturas suficientemente baixas para evitar danificar os circuitos já construídos abaixo. Isso torna possível empilhar as camadas mais de perto e criar conexões muito mais densas entre elas.

Um ponto chave, os pesquisadores dizem, é que todo o processo foi realizado em uma fundição de silício comercial doméstica. “Transformar um conceito acadêmico de ponta em algo que uma fundição comercial possa construir é um enorme desafio,” disse Mark Nelson, vice-presidente de operações de desenvolvimento tecnológico da SkyWater Technology, coautor do estudo. “Isso mostra que essas arquiteturas avançadas não são apenas possíveis no laboratório – elas podem ser produzidas localmente, em larga escala, que é o que a América precisa para permanecer na vanguarda da inovação em semicondutores.”

Ganho de Desempenho e o Que Vem a Seguir para o Hardware de IA

Em testes de hardware iniciais, o protótipo superou chips 2D comparáveis em cerca de quatro vezes. As simulações da equipe sugerem ganhos ainda maiores à medida que o design se torna mais alto com mais camadas empilhadas de memória e computação. Com camadas adicionais, os modelos mostram um aumento de até doze vezes em cargas de trabalho reais de IA, incluindo cargas de trabalho derivadas do modelo open source LLaMA da Meta.

Os pesquisadores também destacam um retorno de longo prazo. Eles afirmam que a arquitetura oferece uma rota prática para melhorias de 100 a 1.000 vezes no produto de atraso energético (EDP), uma métrica que combina velocidade e eficiência energética. Ao encurtar a distância que os dados precisam percorrer e adicionar muitas mais rotas verticais para movimentação, o chip pode aumentar o desempenho enquanto reduz a energia por operação, uma combinação que tem sido difícil de alcançar com designs planos convencionais.

A equipe afirma que a importância do trabalho não se resume à velocidade. Ao demonstrar que chips 3D monolíticos podem ser fabricados nos Estados Unidos, eles argumentam que isso fornece um modelo para um novo período de inovação no hardware doméstico, onde os chips mais avançados podem ser projetados e fabricados em solo americano.

Além disso, eles afirmam que a mudança para a integração vertical 3D monolítica exigirá uma nova geração de engenheiros treinados nesses métodos, assim como a explosão de circuitos integrados na década de 1980 foi alimentada por estudantes aprendendo design e fabricação de chips em laboratórios americanos. Por meio de colaborações e esforços de financiamento, incluindo o Microelectronics Commons California-Pacific-Northwest AI Hardware Hub (Northwest-AI-Hub), estudantes e pesquisadores já estão sendo preparados para impulsionar a inovação em semicondutores americana para frente.

“Avanços como este são, claro, sobre desempenho,” disse H.-S. Philip Wong, professor Willard R. e Inez Kerr Bell na Escola de Engenharia de Stanford e investigador principal do Northwest-AI-Hub. “Mas também dizem respeito à capacidade. Se conseguimos construir chips 3D avançados, conseguimos inovar mais rápido, responder mais rápido e moldar o futuro do hardware de IA.”

Este estudo foi realizado na Escola de Engenharia da Universidade de Stanford, na Faculdade de Engenharia da Universidade Carnegie Mellon, na Escola de Engenharia e Ciência Aplicada da Universidade da Pensilvânia e no Instituto de Tecnologia de Massachusetts, e todas as fabricações foram concluídas na fundição da SkyWater Technology em Bloomington, Minnesota. O apoio veio da Agência de Projetos de Pesquisa Avançada de Defesa, do Programa de Bolsas de Pesquisa de Pós-Graduação da Fundação Nacional de Ciências dos EUA, da Samsung, do Instituto Precourt de Energia da Stanford, da Aliança SystemX da Stanford, do Microelectronics Commons AI Hardware Hub do Departamento de Defesa e da Fundação de Energia dos EUA, e do Programa de Futuro dos Semicondutores da Fundação Nacional de Ciências (2425218).

Os co-autores adicionais de Stanford incluem Suhyeong Choi, Samuel Dayo, Andrew Bechdolt, Shengman Li, Dennis T. Rich e R.H. Yang. Autores adicionais são da CMU e do MIT.